|

Electronics |

|||||||||||||||||||||||||||

|

Digital Transciever Interface

This topic will deal with the issues of how to send a digital data from one point to another point. I will be mostly focus on high data rate technology. So I would not talk much of the common technology you might have heard so often like old type PC Serial Port or Printer port. The purpose of this page is to give you a brief introduction on high speed digital transciever technologies that is becoming more and more of hot topics recently.

Probably this device (or communication method) has been the major issue since the first invention of any kinds of digital devices (including computer and almost all the wireline digital communication).

Brief history of the evolution of the Digital Transciever

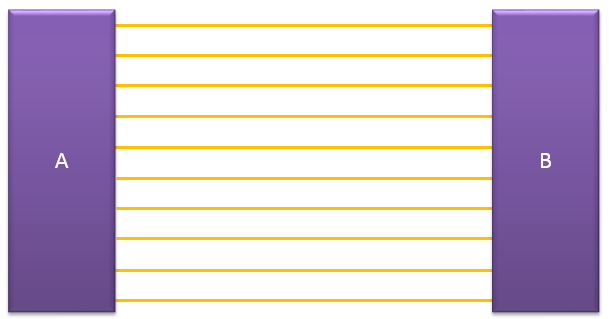

As you can easily guess (or might have experienced by yourself), the first type of digital transciever technology is based on Serial communication as illustrated below. Logically it is just a single electrical line between one point to another point. (In reality, even the serial communication is not a single line. It usually is made up of multiple lines e.g, Tx and Rx lines and ground and some additiona protocol line. However, if you focus only on data line regardless of direction, you can simplify this as a single line as follows)

So far so good. Simple concept and simple design. Then what would be the problem ? Why we needed any further evolution ? It is because of the same reason as in any kind of communication. On day 1, they invent a technology for a certain type of communication and on Day 2 and forever they keep thinking of how to increase the data rate, i.e, how to increase the speed of the communication.

How to increase the data rate ? The first thing you can think of would be just to increase the clock rate of the transmitter and reciever. It is pretty sure that this kind of effort was made at early stage. But the technology at the early stage was not good enough to achieve the enough data rate just by increasing the clock speed.

What would be the next option ? The next option is to transmit the data in multiple parallel lines as shown below. It is like increasing the amount of traffic of cars by widening/adding more lanes on highway. Also, there was another motivation going forward to parallel lines. Most of the diginal processors exchanges data with outside world using multiple parallel I/O pins. So it would be easier to implement the interface between the core chipset and external interface.

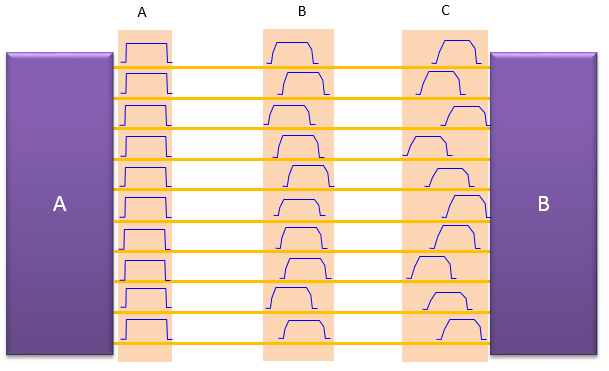

Now you have a new technology implemented. What would be the next question ? Yes, you're right. The same question : How to increase the data rate ?

Theoretically there are more options to increase the data rate comparing to the case of serial communication. The first option would be to increase the number of lines and the second option would be to increase the clock rate. To a certain degree, any of these options would work and there had been evolutions with these options. However, you cannot increase the data rate infinately with these methods. First, can we increase the number of data lines infinately ? Definately the answer is No because we don't have infinate space in any hardware to put the infinate number of data lines. Then, can we increase the clock rate infinately ? You know the answer is No. Comparing to serial communication, there is another problem with the increased clock rate. It is the timing skew issue. By the law of physics, the signal gets destorted and speed of the electric signal varies as it travel along the signal line as illustrated below. At the starting point of the transmitted signal shown at column (A), the signals on all the data line is not distorted and well aligned in time, but as it travel down the signal path, the signal start getting distorted in amplitude and dispersed in timing as you see in column (B). By the time the signal reaches the reciever, the distortion and time dispersion would get so bad that it would cause a lot of decoding errors.

At the end of the eveolution of the parallel communication, we have a question of how to remove the timing skew and as energy efficiency of the system gets more and more important we get to have another question 'how to drive this communication system at a very low energy concumption ?' meaning 'How to maintain the reliable decoding at very low driving voltage ?'

Do we have any answer to these questions ? Yes, we have. Ironically, the answer is 'Going back to our old friend ; Serial Communication'. Then you may ask 'How the old fashioned serial communication can solve these problems ?'. Actually, it is not only the serial method itself that solves these problem. There has been drastic improvement in semiconductor technology to help the solution working. It would be obvious (easy to understand) on how serial communication can solve the timing skew issue. Of course, there still be a certain degree of time dispersion (delay spread) on serial data line, but at least you don't have to worry about the synchronizing these dispersed signal among multiple data lines. Also there has been another very important evolution in the area of semiconductor. The transistor switching speed has become lightening fast and the driving voltage drop has continually evolved.

Another important invention that has helped the improvement is Balanced signal (Balanced Circuit) as illustrated below. This helps the serial communication not only in terms of lowering driving voltage but also in terms of the resistance to noise.

With this invention, we would have the same question again. How to increate the data rate ?

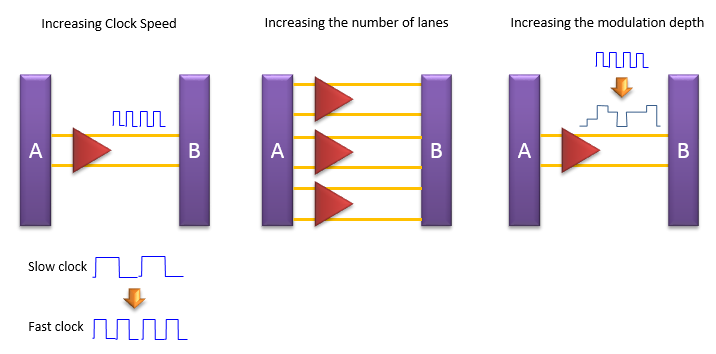

The most common methods that are employed are roughly three types as illustrated below. The first method is obvious. Just to increase the clock rate. The second method is also what anybody can guess. It is to increase the number of lanes. This is not the parallel communication. It is multiple separate serial communication. The third one would not be what many of digital people would have thought, but it is one of the most common techniques to be used to increase the data rate in Analog or RF communication. It is to apply high depth modulation scheme like PAM4, PAM8 or 16 QAM etc.

Since the rebirth of the serial communication, we have seen ever evolving serial communication method for the past decades and this evolution continues even now .. and now (as of 2015) we are talking about 400 Gb communication. (I will write further on these new evolution later in this page or post a new page). In this evolution, these three methods are employed in various combinations, meaning in some case only one specific method (e.g, increasing clock rate only or increasing the number of lanes only) and in some other case two or more methods are applied in combination. Followings are some of the examples of this evolution.

Technology components of Digital Transciever

In some sense, what I have described above is just with an aspect of a concept, it is not about real hardware. When it comes to implementing those concepts, it would boil down to an electronic device or circuit. In this section, I will describe on various type of electronic device or circuit that are used to implement the technologies described above.

Most of the conetents of this page is based on an Whitepaper from Altera (Ref [1]). I will add additional contents as I learn more.

TTL(Transistor to Transistor Logic) :

Low Voltage TTL (LVTTL) :

ECL(Emitter Coupled Logic)/CML(Current Mode Logic) :

PECL(Positive Emitter Coupled Logic) :

LVDS(Low Voltage Differential Signaling) :

LVPECL(Low Voltage Positive Emitter Coupled Logic) :

PCML(Pseudo Current Mode Logic) :

HyperTransport Technology I/O :

PCI Express (also known as 3GIO and Arapahoe) :

Reference :

[1] The Evolution of High-Speed Transceiver Technology - Whitepaper, Altera [2] Multi-Gigabit SerDes: The Cornerstone of High Speed Serial Interconnects

|

|||||||||||||||||||||||||||